# GOVT. POLYTECHNIC BALASORE

### [LECTURE NOTE]

### VLSI & EMBEDDED SYSTEM TH 2

DIPLOMA

5<sup>TH</sup> SEMESTER, E & TC ENGINEERING

PREPARED BY:-ER. YOGASAKTI YOGAMAYA (Lect. In E&TC)

DEPT. OF ELECTRONICS &TELECOMMUNICATION ENGINEERING

### Com

### Historical Perspective:

As more a more complex functions are required in various data processing a telecommunication devices, the need to integrate these functions in a small package is also increasing.

ogates in a monolithic chip has been raising due to rapid.

progress in processing technology & interconnect technology.

| Ena                                | Year Date                     | Complexely (# of logic blocks<br>per chip) |

|------------------------------------|-------------------------------|--------------------------------------------|

| single Triansistor                 | 1958                          | The only to                                |

| unit logic (one gate)              | 1960                          | 1 may 20 1 may 20 1 m                      |

| Multifunction                      | 1962                          | 2-4                                        |

| complex fearction                  | 1964                          | 5-20                                       |

| Medium Scale Integration (MSI)     | 1967                          | 20-200 . 500                               |

| Large Scale Integration (LSI)      | 1972                          | 200 - 2000                                 |

| very large seals Integnation ( VI. | SI) 1978                      | 2000- 20,000                               |

| ULtra large seal Integration (UL   | -61) 1989                     | 2000 - above                               |

| N .                                | A TOTAL TOTAL CONTRACT OF THE | 7                                          |

If the monolithic integration of a large number of functional on a single chip usually provides:

- -> vers area / volume & therefore comportner

- -> Less power consumption

- > Less testing requirements at system level

- or Higher reliability, mainly due to improve on chip interconnects

- -> Higher speed, due to significantly reduced interconnection length

- -> Significant cost savings

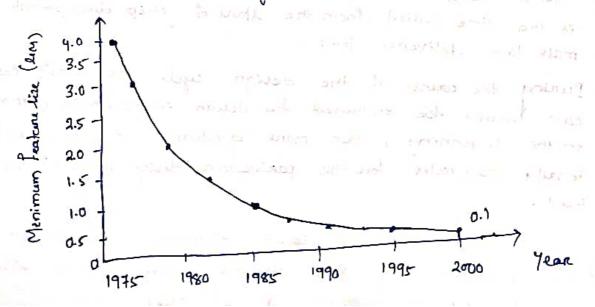

- -> Advances in device manufacturing technology allow the steady reduction of minimum feature size (such as minimum channel length of a transsistor on an interconnect width realizable on chip)

- -7 Memory cercuits are highly regular, & thus more cells can be integrated with much lux area for interconnects.

- 7 Digital emos Ic, have been the driving force behind VLSI for high penformance computing a other scientific & engineering application

- In demand for digital cases ICA will be continuously strong due to salient features such as low power, reliable performance, chacit techniques for high speech using dynamic cincuits & organizery improvements in practicity technology.

- improvement in prawing technology.

The Now the minimum feature size in comes I've can decrease to 0.035 lum (35 nm). With such technology, the level of integration in a single chip can be on the order of several tens of billions of transistors for logic chips on even higher in case of memory chip.

1 The Contraction That The T

and the world offered the contract

# VLSI Design Methodologies:

- The logic chips such as microprocusion chips a Digital signal photography (DSP) chips contains large arrays memories a different functional centre. Thus their design complexity is consider much higher than that of memory chips.

- The design complexity of logic chips increase almost exponentially with the number of transistors to be integrated.

- Thin is translated into an increase in the design eyels time, which is the time personal from the start of this development until the mask-tape delivered time.

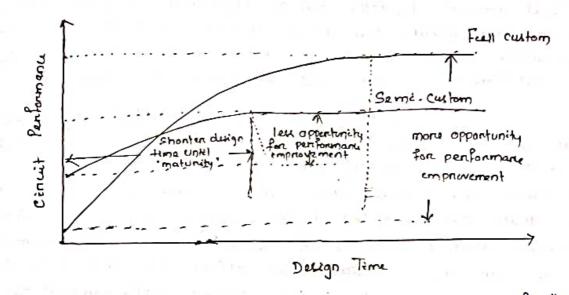

- Journal the course of the design cycle the circuit performance can usually be increased by design improvements; more rapidly in the beginning, then more gradually until the performance finally saturates for the particular design style & technology being used.

the level of cincit performance which can be reached within a ceretain design time strongly depends on the efficiency of the design methodologic as well as design Style.

- Here two different VLSI design styles are compared for their relative relative mercits in the design of the same product.

feell-coustom design style (where the geometry 2 the placement Using the optimized individually) requires a longer can be Inansulon every maturity can be reached, yet the inherent delign ontil time admost every aspect of cincuit delign of adjusting flexibility penformance emprovement during cencuit oppertunity For for more delign style.

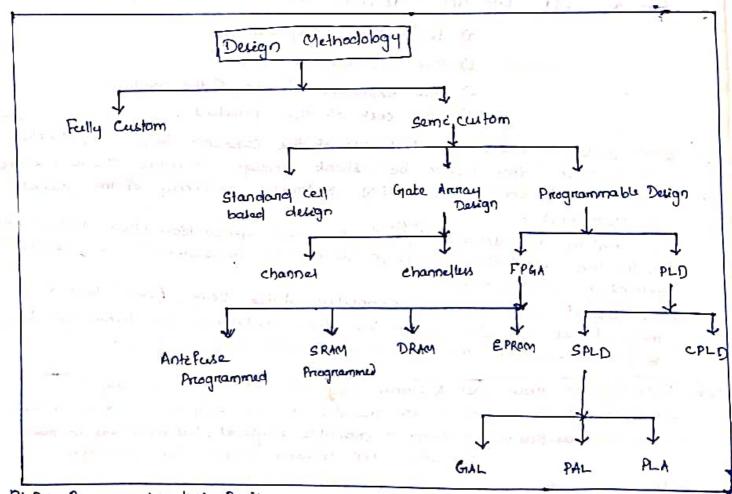

PLD: Programmable logic Device

SPLD: Simple programmable logic Device CPLD: Complex n 11 h

GAL: Gate herrey togic PAL: Programmate array logic in the final product typically has a high live of performance (e.g. high procusing speed, low power discipation) & the silicon area is relatively small because of better area utilization. But the comes at a larger cost in terms of design time.

standard - cell based design on Front ) will allow a shorter duign time until design maturity can be achived.

is not the early during phase, the circuit performance can be even higher than that of a feet - custom during, since some of the components used in Semicustom design are already optimized. I but the semicustom design style offens hus appendicultly for performance improvement, & the overall performance of the fenal product will inevitably be less than that of a fell-custom during.

for a visi product depends on the periformance requirements, the technology being asent

for a VLSI Product depends on

a) Performance Requirements

b) The technology being used

c) The expected lifetime of the product

d) The cost of the product.

of orders to make the best use of the current technology, the chip development time has to be short enough to allow the manufacture maturing of this manufacturing & timely delivery of the product to customers.

As ruality, the design style of the next generation this usually overly with the production type of the turnent generation thereby assuring continuity.

The use of sophisticated computer fided Design (cAD) tooks & methodologicus are also essentiaul fore reducing the duign cycle time & fore managing the increasing durign complexity.

Note: Feelly Custom: Here each a every paret of CKT will be duign.

Semicoustom: All components are available a we'll only connect to get a duice standard (e1) best Design: Nothing is available physical, but everything in paper.

Ex: Book. Cell library produced by fabrication

Giate armay Design: Something in available physically.

Programmable Design: Everything available in physically is we only write

the pringram for aparation

# VLSI Design Flow:

Structural Domain Behavioral Domain Processori ALgonathm Finite state Machine /RTL language Register ALU / RTL Leaf Call Gate Descriptor / Boolean Equation Module Translator Differential Equation Mark / Polygo cell plaument/ stick Module plaument / standard Cell chep floorplan Geometrical Layout Domain

Fig: Simplified VLSI design flow in three domains (Y-chart Representation)

> The design prouse, at various levels, is usually evolutionary in nature of the starts with a given set of requirements. Initial design is developed a tested against the requirements.

of such improvements are not met, the design has to be improved.

of such improvement in either not possible on too costly, then a

revision of requirements & an impact analysis must be considered.

The Y chart introduced by D. Gajski illustrates a simplified design flow for most logic chips, cuing design activities on three different axes (domains) which resembles the letter Y.

The Y-chart consists of three domains of representation namely is Behavioral domain.

it Behavioral domain on Functional domain

il) Structural domain

in) Geometrical layout domain

- The design flow starts from the <u>algorithm</u> that describes the behavior of the target chip. The corrusponding architecture of the <u>proumor</u> is first defined.

- 7 9+ 11 mapped onto the chip sunface by floriplanning.

- The next design evolution in the behavioral domain definer finite state machines (FSM) which are structurally implemented with functionally modules such as regesters & arithmetic logic Unit (ALU)

- There modules are then geometrically placed onto the chip senface wing CAD tools for automatic module placement followed by routing, with a goal of minimizing the interconnects area a signal delays.

- -) The thered evolution starts with a behavioral module description.

- -) andividual modulus are then implemented with leaf cells. At this sleege the chip is described in terms of logic gates (leaf cells), which can be placed a interconnected by using a cell placement & nouting program.

- The last evolution involves a detailed Bootsen description of hafcelle followed by a transistor level implementation of hafcell & mask generation.

- 790 the standard cell based design style, leaf cells are pre-designed (at the transiston level) & stored in the a library for logic implementation, effectively eliminating the need for the transistors level design.

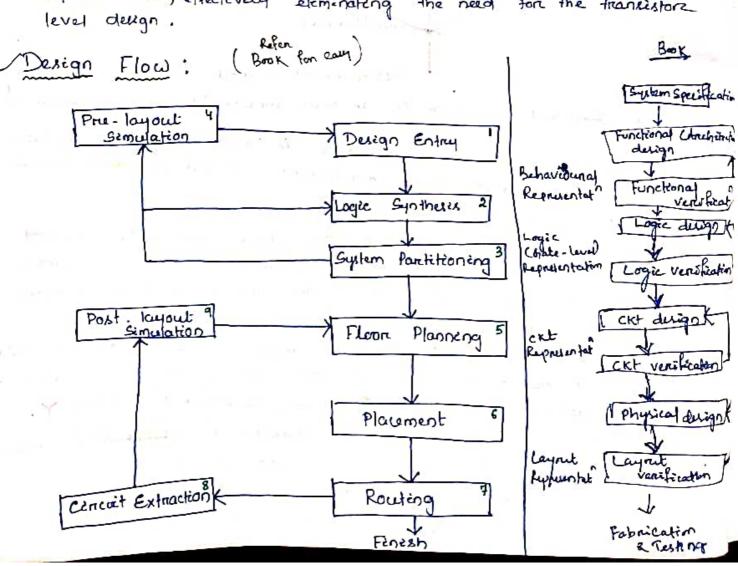

- 1. Design Entry: Enter the design into an Asic (Application specific Ic) design system either using a HDL on schematic table.

- 2. Logic Synthesis: Use an HDL & logic synthesis tool to produce a net lest i.e description of logic (ell & their connection

- 3. System Pantikoning: Divide a lange system into Asic size pieces.

- 4. Prelayout Simulation: Check to see the design function connectly.

- 5- Flour Planning: Arriange the blocks of the net list on the chip. on, 9t describes the interconnection of the blocks (RAM, ROM, ALU etc) logic cells (NAND, NOR, Flf.et) withtn the blocks & the logic cell connectors.

- 6. Placement: Decide the location of cell on the block.

- 7. Routing: Make connection between cell & & blocks.

- 8. Cencuit Extraction: Determine the rusistance a capacitance of the interconnets .

- 9. Post layout Simulation: check to see the design still works with the added loads of the interconnects.

\* Step 1-4 are parts of logic design & step 5-9 are pants of physical delign.

# Design Heenanchy:

- of the use of the hieranchy on "divide & conquer" technique involves dividing a module into sub-modules & then repeating this operation on the submodulus until the complexity of the smaller parts becomes manageable.

- 3 this approach is very similar to software development Where tarrege consignams are split into smaller & smaller Section until simple submoutines, with well-defined functions & interfaces. can consiller

- I The design of a VLSI chip can be represented in three domains. Cornespondingly, a heerearchy structure can be described in each domain separately.

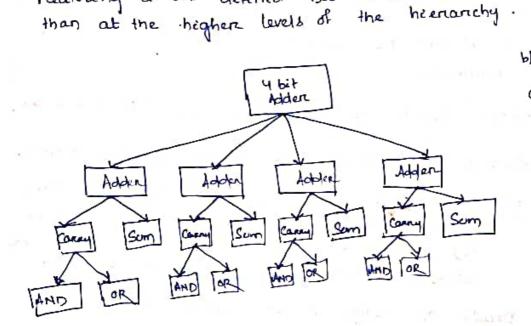

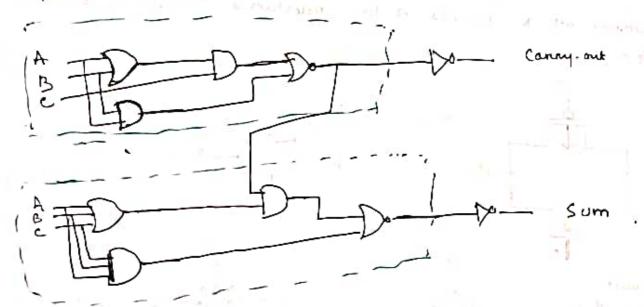

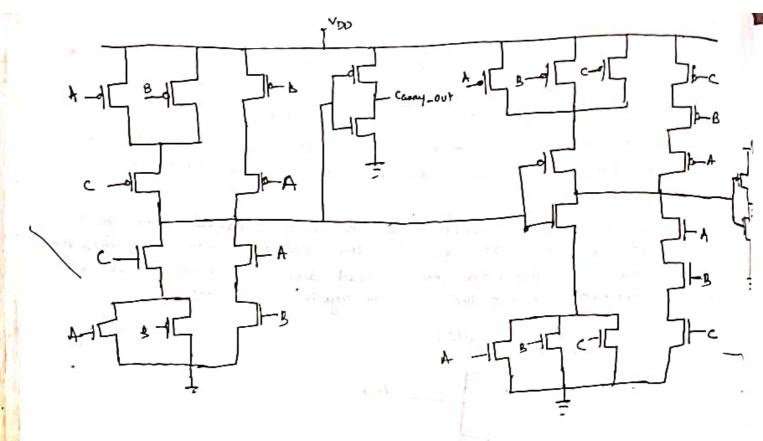

- of Example of structural hierarry shows the structural decomposion of a cours 4 bit adders into its components

Anne adden can be decomposed prograssively into 1 bit addens, separate carry & sum circuits & finally into individual logic gates.

7 At this lower level of hierarchy, the duign of a limple circuit realizing a well defend Boolean function is much easier to handle

(Structural decomposition of a 4 bit adder, showing the levels of hierarchy)

into its various functional blocks will provide a valuable quick for the actual realization of these block on the chip. Obviously, the approximate shape a size (area) of each sub-module should be estimated in order to provide a useful florenplan.

P SUM -S

a Canry - Co

# Loncepts of Regularity, Modularity & Locality:

- \* Regularity means that the hierarchical decomposition of a large system should rusult in not only simple, but also similar blocks as much as possible.

- onsisting of identical cults such as a parallel multiplication armay.

- 7 Regularity can exist at all levels of abstraction. For example, at the transiston level uniformly sized transistons Limplify the duign 2 at the logic level, identical gate structure can be used.

It Modularity in design means that the various functional blocks which make up the langua system must have well-defined functions a intenferor.

- Modularity allows that each block on module can be deligned relatively independently from each other, line there is no ambiguity about

the function & the signal interfol of these blocks.

- of the blocks can be obtained combined with ease at the end of the design process, to form the large system.

- The concept of modularity enables the panallelization of the design process.

ach module in the system, we effectively ensure that the internal of each module become unimportant to the extensor module. Internal details remain at the local level.

In the concept of <u>locality</u> also ensures that connections are mostly between neighboring module, avoiding long distance connections as much as possible.

or many last point is extremely important for availing long interconnect delays.

VLSI Design Stylus

Field Programmable Gate Array (FPGA):

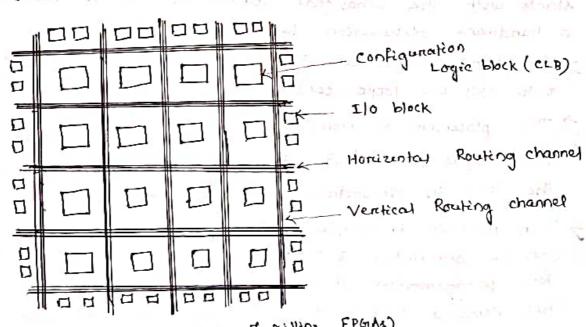

(General architecture of Xillinx FPGIAs)

Feelly tobricated FPGA chips containing tens to hundreds of thousands, on even more, of logic gates with programmable interconnects are available to users for their enton handwere programming to realize during functionality.

- This design style provides a means of for fast prototyping a also for cost-effective chip design, especially for low volume applications

- A typical field programming gate array (FPGH) chip consists of IIO buffers, an array of Configurable logic blocks (CLBS), & programmable interconnect structures.

- The programming of the interconnects is accomplished by programming of RAM cells whose output som terminals are connected to the gates of Mos pass transistors.

- Thus, the signal mouting between the CLBS & the Ilu block is accomplished by setting the configurable switch matrices according

\* The complexity of a FPGIA chip is typically obtenmined by the number of CLBs it contains.

- + State of the art FPGA chip can also support system clock frequency cepto boundneds of MHZ.

A The typical design flow of an FPGA Chip stants with the behavioral description of the functionality, viling a handware description language ray VHDL.

The synchronized architecture then technology mapped (On patitional)

- into extr on logic cells:

- 7 The placement a mouting step airigns individual togic cells to FPGA Sites (CLBs). & determines the nouting patterns among the cells in accordance with the net list.

- After renting in completed; the on chip persformance of the duign can be simulated a verified before about loading the design for programming of the FPGM chip. The programming of the Chip remains valid as long as the chip is powered on, or until it is reprogrammed.

It the largest advantage of FPGA based design is the very short turn around time, i.e the time required from the start of the design process until a functional chipis available.

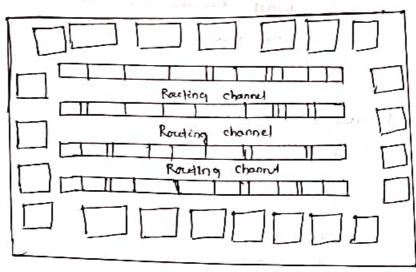

# Gate Armay Design:

- -> Gate array implementation requires a two-step manufacturing prous.

- 7 The first phase, which is based on generic (standard) masks, rusult in an array of uncontred transcitors on each GA chir.

- 7 A corner of a gate armay thip contains bonding pads on its left a bottom edges, diods for 110 protections noons pros transistors for chip output driver circuits adjount to bonding pack, arrays of non, pros transistors, underpass were segments! & power a ground buses along with contact windows.

- > Typical GA platforms allow dedicated areas, called channels. for interest mouting between nows & columns of Mos transisters

- -> The availability of these nouting channels simplifies the interconnections.

- -> Interconnection pretterns that perform togic basic logic gates can be stored in a library, which can then be used to automize rows of uncommitted transiston acording to the netlist.

- -> Some of the philonon offen dedicated memory (RAM) arrays to all as higher deneity.

of 90 modern GAs, multiple metal layou are used for channel nouting. With the use of multiple interconnet layers, the nouting can also be achieved over the active cell nouting channels can be removed as in arucu, thus the

of Here the entire thip sunface is covered with Uncommitted

nonos a proces transistors.

-> For intercall mouting, some of the uncommitted transistors

of The GA chip Utilization factor, as measured by the used (bannellus)

thip area divided by the total chip area.

Standard - Cells Based Design: -> The standard cells based design is the most prevelent fullcurion design styles which/ requires development of a fall curion

of state the standard / will in also called the polycell.

-> 90 this design style, and of the commonly used logic cells are developed, charuterized & stoned in a standard cell library.

- > The standound call is also called polycell.

- I an this design style, all of the commonly used logic cells are developed, characterized, a storted in a standard cell library.

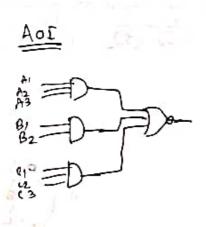

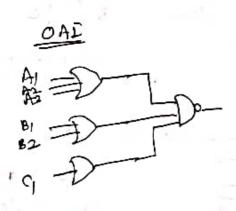

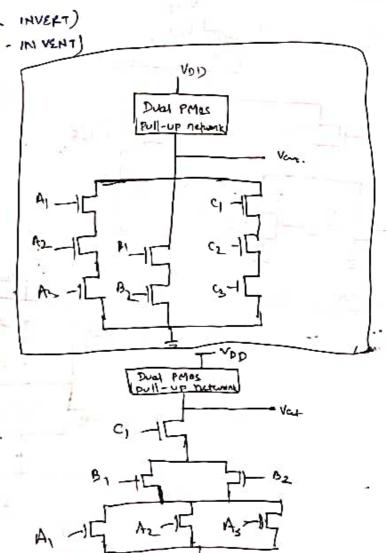

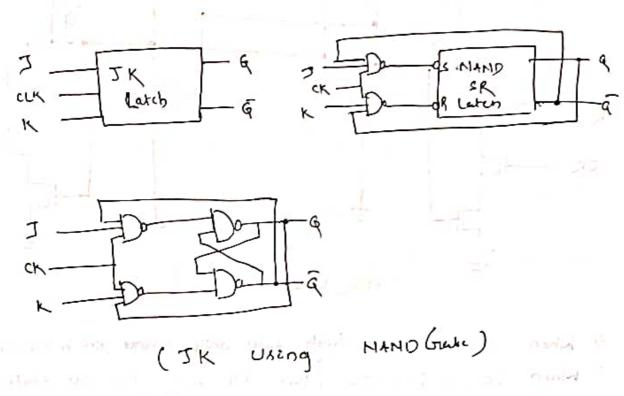

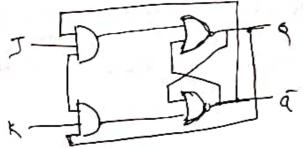

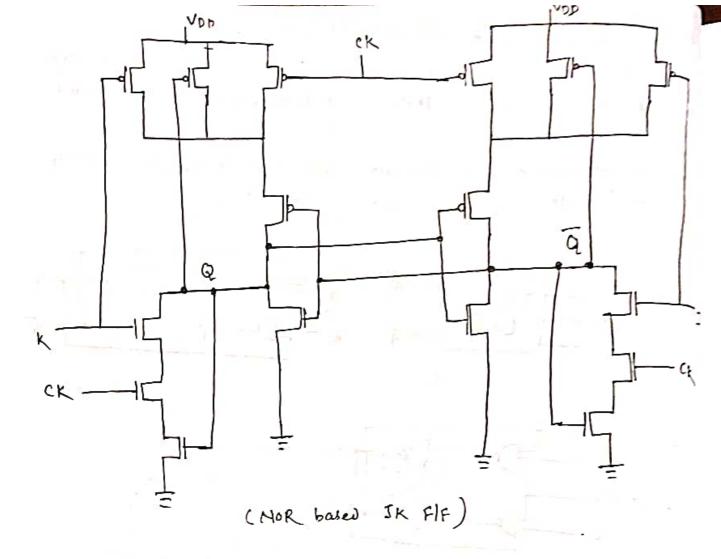

- The A typical Library may contain a few hundred cells including inventors, NAND Gates, NOR gates. complex AOI, OAI gates, D latches, a flip flops.

- -> Each gate type can be implemented in several vertions to provide adequate driving capability for different fan-outs.

- 7 Each cell is characterized according to several different characteric -zation categories, including

- \* Dalay time Venue load Capacitance

- \* Cincit Simulation model

- \* Timing simulation modes

- \* Fault Simulation model

- \* Cell data for place & noute

- \* Mark data.

- To enable automated plaument of Cells & nouting of inten

( Cell Connections, each cell layout is designed with a fixed height. So that a number of cells can be abutted side by live to form nows.

- The power a ground rails typically run paralled to the Upper & forwer boundaries of the CUI, thus neighbouring Cells Share a common power bus a common ground bus.

- The input a output pine are located on the upper a lower boundaries of the cell.

- The nmos transistors are located closer to the ground rail while the pmos transistors are placed closer to power rail.

- The chip area contains now t columns of standard cells. Between cell nows are channels are for dedicated intental nouting.

- The eight delay, noise mangins, a power consumption of each cell should be also optimized with proper Sizing of transistoris wing ckt simulation.

- Joss a number of cells must share the same input endlor output signals; a common signal bus structure can also be incorporated into the standard cells based this layout.

- I Within the cell block, the separation beto neighboring nows depend on the numbers of wines in the recuting Channel between the cell rivio.

other, rusulting in a smaller chip area.

ROOM COOK

( A Simplified floorplan of standard cells based duign)

# Full Custom Design:

- 790 a truly feetly- custom design, the entire mark design is done anew without use of any library.

- The development cost of such a during style is becoming prohebitively his. Thus the concept of during recure is becoming popular in order to reduce during cycle time & development cost.

- of memory (el), be it static on dynamic.

- The logic chip design, a good comparting can be achieved by wing a combination of different design styles on the same chip, such as standard cells, data-path cells, & priorgrammable logic arriers (Pub).

- 790 rual ted cutom layout in which the geometry, orientation, a plaument of every transistor is done individually by the duigner, designer productivity is usually very low typically

- -> 9n digital CMOS VLSI, feell-custom durign is namely used due to the high labore cost.

- -> Ex of hybrid feel custom design is 9nfel Pentium Sup chip.

### \* Compuler Aided Design Technology: -> Computer Aided duign (CAD) tools are essential for timely development -> Although EAD took cannot ruplace the enative a inventive parts of the design activities, the majority of time-consuming a computation Entensive mechanistic points of the design can be executed by using The CAD technology for VLSI Chip design can be catagonies into the following areas: High level Synthesia . H. Logie · Synthelis | H. Ckt Optimization M Layout Ale lanchous Simulation ( ) (apint mind & Design rules checking \* Formal Verification tes 11 Culliam Syntheis Pools: - The high level synthesis took using handware discription

languages (HDLs). such as VHDL OR Verilog, address the automation of the durign phase in the top level of the durign of with an accurate estimation of lower level during style feature, Such as chip area a signal delay, it can very effectively determine the types & quantities of modules to be included in the chip disign.

-> Many tools are customized for particular during needs, especially fon area minimization, low powers, high speed on this creighted combination

- The took for cut optimization are concern with transiston living for minimization of delays a with process variations, neith a reliability hazands.

- -> The layout CAD tools are good driver a include some digne of aptimization functions.

- -> The layout cap tools include floor planning, place & noutine, & module generation.

- To achieve an optimum on near optimum placement of all standard cells on chip, so the signal routing bet the cells can be accomplished with minimum interconnect area a minimum delay.

- Tonce the physical locations of all the cell. In a delign are determined an automatic routing tool is used to create the metal interconnections between the cell terminals, based on the gate netlist.

### Simulation & Verification Tools:

The simulation category, which is the most mature area of VLSI CAD, includes many tools ranging from ckt level simulation timing level simulation, logic level simulation a behaviored simulation.

- The aim of all simulation CAD tools is to determine if the designed och meets the required specifications, at all stages of the design process.

- of the ckt, i.e to determine if the designed ckt actually has the designed logic behavior.

- output patterns.

moutinely used to determine nominal a worst ease gate delays to identify delay - critical signal paths on elements, a to predict the influence of panalitic effects upon out behavior.

\* The design nules checking can category included the tools for layout nules checking, electrical nules checking, & ruliability rules checking.

A The Committee has a second of K

# Fabrication of Mosfet

### Introduction:

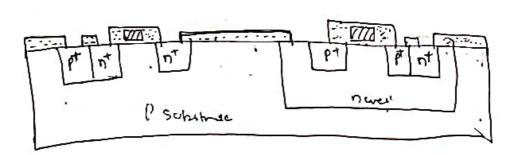

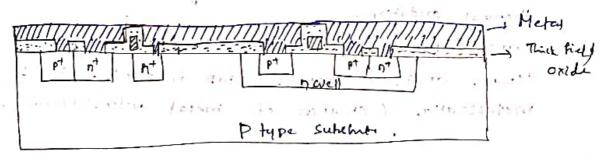

- -> A well- established cryos Pabrication technology requires both n. channel (nmos) & p. channel (pmos) transistors be built on the same thip substrate.

- → To accomodate both nmos & pmos devices, special rugion must be cruated in which the semiconductor type is opposite to the substrate type. These regions are called wells or tubs.

- -> A pewell is cruated in an ntype Substrate on viu-verse,

- -> 90 twin-tub cmos technology, additional tubes of the sametyk as the substrate can also be created for device optimization.

### tabrication Process; Flow:

Basic Steps: MONEY HAMIXEPATION:

### Notu:

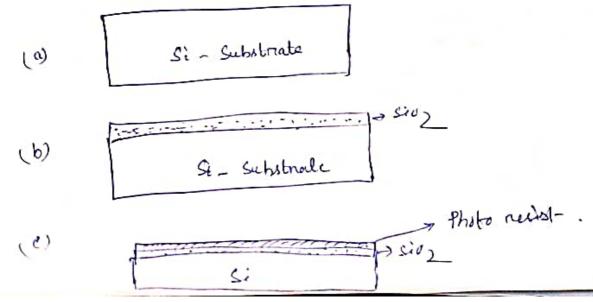

- 7 The integrated cut may be viewed as a set of patterned layers of doped silicon, polysiticon, metal a insulating silicon dioxide.

- -> 9n general, a layer mut patterned before the next layer of material ig applied on the chip.

- If The prouse used to transfer a pattern to a layer on the chip in called "Lithography"

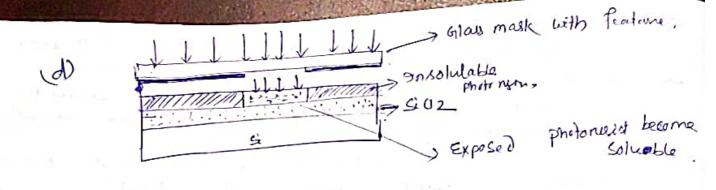

\* The Sequence stants with the thermal Oxidation of the silicon sunface, by which an oxide layer of about I may thickness (B)

- of The entine oxide surface of then covered with a layer of photorwist, which it essentially a light sensitive, acid-recistant organic polymen, initially insoluble in the developing solution (C)

- 79f the photorusist material in exposed to Ultraviolet (UV) light, the exposed areas becomes soluble so that they are no longer ruintant to etching solvents -

- of the area on the surface with a mark during exposure.

- -> When the structure with the mask on the top is exposed to UV light, and which are covered by the opaque features on the mask are shielded.

- -> 90 the areas where the UV light can pass through, the photorucist is exposed & becomes soluble. (fig.d)

ensoluble a becomes soluble after exposure to UV light is called positive photorulists.

- often exposure to uv light, called negative photonuist.

- Thegative photomuists are more sensitive to light, but their photo lethographic resolution is not as high as their of positive photomuists. Therefore negative photomuists are used less commonly in the manufacturing of high density integretal ckt.

pontion of the photoruist can be rumoved by a Rollvent.

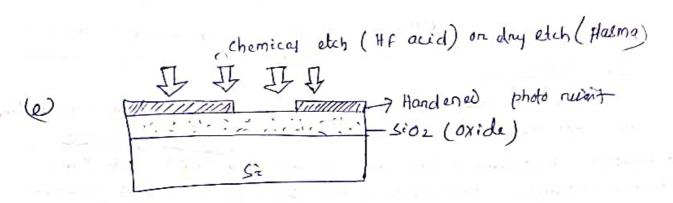

The silicon dioxide regions which are not covered by handened photorusist can be eather away either by using a chemical solvent (it away) on by using a drug etch (plasma etch) prouss. (fig e)

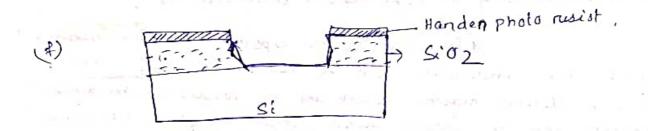

The remaining photoruist can now be stripped from the silicon the remaining photoruist can now be stripped from the salicon

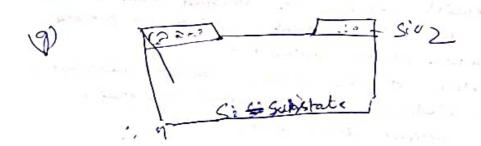

The remaining photorius can have bearing the patterno dioxide sunface by every another solvent, leaving the patterno sivilen dioxide feature on the senton fig 9)

sub-micron device, electron beam. (E-beam) Litrography is

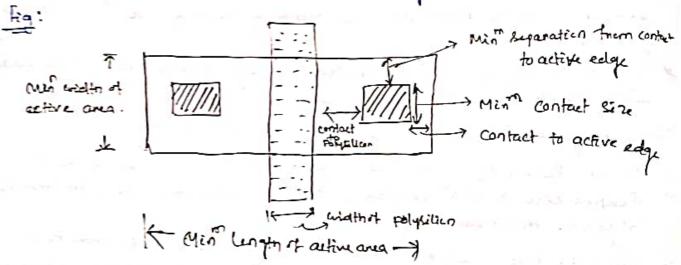

Fig:

- 1. Prousing is carried out on a thin water cut from a single crujstal of silicon of high purity into which the required Pimpunites are introduced at the crujstal in grown.

- 2. A layer of silicon dioxida (5102) typically I ham thick is grown all over the surface of the water to protect the surface, act as a barrier to dopants during procuring, & provide a generally insulating hubstrate onto which other layer may be deposited a patterned.

- 3. The sunface is now covered with a photoresist which is deposited onto the water a spun to achieve an even distribution of the required thickness.

- 4. The photoreeist layer is then exposed to offre violet though through a mask which defines those regions into which diffusion is to take place together with translation channels.

- 5. There are an subsequently readily atched away together with the underlying silicon dioxide so that the water sentes is exposed in the window defined by the mask.

- 6. The remaining photoruist is removed & a thin layer of side is grown over the entire this surface & then the polycilicon is deposited on top of this, to form the gate structure. The polycilicon layer consists of heavily doped polycilicon deposited by the micest vapour deposition (CVO). In the falorication by the micest vapour device, precise control of thickness, of the fine pattern device, precise control of thickness, conquerity concentration & restistively is necessary.

- 7. Further photonuist coating a marking allows the polytilical to be patterned (as step 6), & then their oxide is rumoved to expose areas into which in type impunition are to be differed to form the source a drain as shem. Differing is achieved by heating the wafer to a high temperature a passing a gas containing the durined in type impunity a passing a gas containing the durined in type impunity over the sunface. The polyticism with undurlying than over the sunface. The polyticism with undurlying diffusion—oxide & the thick oxide act as masks during diffusion—the processity self-aligning.

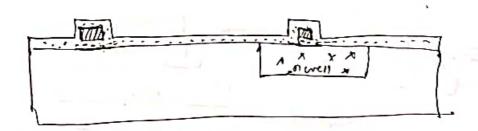

- 8. Thick Oxide (SiO2) is grown over all again & in then masked with photonerist & etched to exposed Selected areas of the Polypilican gate & the drain & sounce areas where connections are to be made.

- 9. The whole Chip then has metal (alterninium) deposited one its senface to a thickness typically of lum. This metal layers is then marked & etched to form the required interconnection pattern.

The process revolves around the formation of deposition & patterning of three layers, separated by silicon dioxide insulation. The layers are diffusion circuin the substrate, polycilicon on order on the substrate, & metal insulated again by oxide.

again by oride. Substnate Thick oxide (1 em) Photomist Mask (4)

6 Window in oxide Patterned Poly (1-2 km) on thin oxide (800 - 1000 A) of the samplement of the to Confact hole (cuts) (8) patterned Metallization (almeeninem (14m)

# CMOS Fabrication:

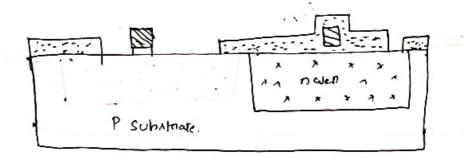

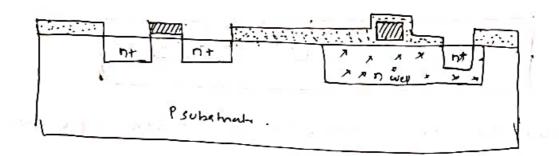

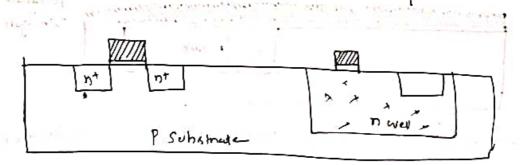

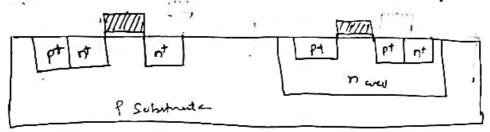

### The n. Well Prouse:

The well ecros extrane superior to powell because of the lower substrate bias effects on transiston thrushold voltage & inherently lower parasite capacitances associated with sounce & drain region.

# Typical in well fabrication steps are:

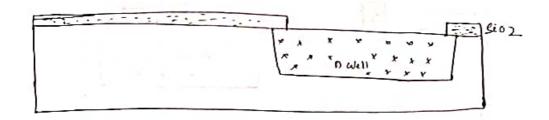

- -) The let mark defines the n-well reagions. This is followed by a low dose phosphonus implant driven in by a high temperate differion step to form the -n-wells.

- Pt disfusion breakdown without companying the news to not mask separation.

- The next steps are define the devices & diffusion paths, grow field oxide, deposite & pattern by the polytilian, cannyout the diffusions, make contact cuts, & finally mentallize as hely.

used to define the n-2 p-diffusion regions respectively. These same masks also include the VDD 2 Vss contacts respectively. I an overly process. creates non-appearing planned Characteristics.

Steps:

\*\*\*

Formation of n-well regions

Define nMos a Pmos active

Reld a gate oxidation (thinox)

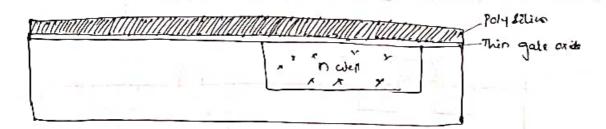

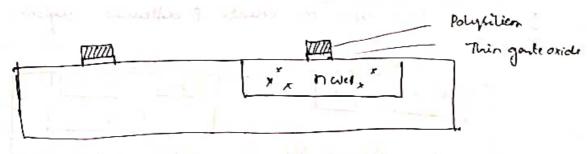

Form a Pattern Polysidion

pt diffusion

Contact cuts

Deposite a pattern metallization

Over glass with cuts for bonding Pads

6. n. well is formed using diffusion on ion implantation.

7. Strip off remaining oxide using HF. Subsequent step we the same photo lithography process.

8. Deposite then layer of Oxide. Use CVD to form poly & dope havily to increase conductivity.

9. Pattern poly using the previously discussed photolithography prom.

10. Coven with oxide to define of differior regions.

12. Diffusion on ion implantation used to create or diffusion regions.

13, Strip off the Oxide to complete postering step.

14. Similar. Steps www to create P diffusion regions

15. Coven chip with thick field oxide & etch oxide when contact cuts are needly

15. Remove Excus metal Ceaving wine:

# CMOS N- Well Fabrication Proces flow:

- A Well established cmos tabrication technology requires both n-channel (n-mos) & p-channel (p-mos) transistors be built on the same chip substrate.

- To accomodate both n mos & P Mos devices, Special tregion must be cruated in which the semiconductor type it appears to the substrate type. These regions are called wells on tube.

- -) A p. well ex created in an ntype substricte on viu-verya

- > A twin-tub . emos technology, additional tubes of the same type as the substrate can also be created for device optimization.

The simplified proves sequence for the fabrication starts with the creation of the n-well region for pmos transiston, by impurity implentation into the substrate.

Then a thick oxide is grown in the region surrounding the nmos & pmos active region.

- +) The thin oxide is subsequently grown on the surface through thermal oxidation.

- or There steps are followed by the creation of ort & pt regions (Sounce, drain & channel - stop implants) & by final metallization - (cruation of metal inter-connects).

Steps: 米米木

icali monde achazonycy. Now a 10th.

gat surjust actionals to the contract to the contract of so supported to the second of the control of the co . Moninger. 1 and some set on Almet.

to accompany to a sout through the cat i attachananan est fablic no tateur ad disem inspire anti sucretion are to a sale openitions also be directly - - -

entities as standard a soft of the same first and the first of the

emed the late of the temporal experienced toward definition of the with all alterior

a so to insign

replaced rearries, remaid designificant real. K A Ten 11-2 Anne de la Maria de la Carta de all the policies of the property of activities being and

propries in the state of the state of the state of the state of

The state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the s

Scilar

General Concept:

The Fermi potential Qr, which is the function of temperature & doping, denoted the difference between the intrinsic fermilevel Ei & fermilevel Er.

$$Q_F = \frac{E_F - E_i}{q}$$

For p type Semiconductor. The ferent potential can be approximate by:

For n type Semiconductor, Fermi potential can be given by

$$\Re F n = \frac{kt}{9} \ln \frac{ND}{Di}$$

Where K7 Boltzmann constant

9, - The Unit (electron) Charge

ni 7 Intrinsic carrier consentration

T -> Tempenature.

MA + Accepton (Bonon) Concentration

ND- Donor conuntration

He The electron affinity of silicon, which is the potential difference (four species) between the conduction band level & vaccume level, is denoted by ax.

I The energy Required for an electron to move from the Fermi level into free space is called wark function 90s.

Whene Ee = conduction band level .

If Fermi level: The fermilevol (EF) is the maximum energy level which is occupied by an electron at absolute the too (OK) temperature.

The fermi level lies at the middle of the forbidden energy gap.

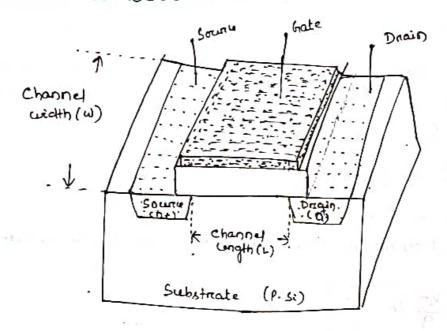

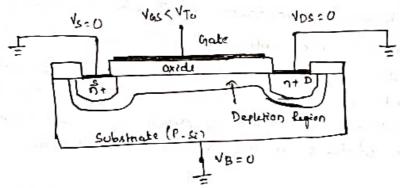

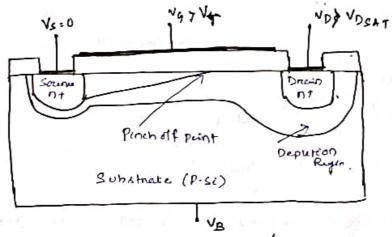

( fig: The Physical Structure of an n-channel enhancement type Masfet)

The basic structure of an n-channel Mosfet is shown above figure.

- \* 9+ is a 4 terminal device constitute a ptype substrate, in which two nt differior region, the drain & the sounce are formed. The sunface of the substrate region bet the drain & source is formed covered with a thin oxide layer, & the metal (or polycition) gate is deposited on the top of this gate dielectric. The two nt regions will be the current-conducting terminals of the durie.

- The distance bet drain & Sounce differsion region is the channel length 'L' & the lateral extent of the channel is the channel width 'w'. The thickness of the oxide larger Coverring the channel is region is "tox!

- A mos transistore which how no conductions channel region at zero bias is called "Enhancement type Mosfer" of a conducting channel already exists at zero bias gate bias, the device, is called a depletion type Mosfer. On a Mosfer with p-type substate on the Sunface of Arction region, the channel region to formed substrate of the sunface is nearly . The such type a device with p-type substrate of called n-channel Mosfer. For the usual p-channel substrate of called n-channel Mosfer. For the usual p-channel substrate of a lower potential than the other not region, the drain.

VOST DRain to " "

-: NBS-> Substante to " ?

(: B + Substrate)

device is: Control the current conduction between the sounce a tree drain using the electric field generated by gate voltage as a control variable.

(formation of a depletion region in an orchannel enhancement type (MOSFET).

When bear condition is applied across an enhantment type mosfer, the source, the direction is the substitute terminals are connected to ground. A positive solver is applied to gate to create the conducting channel underneath the gate. For small gate vollage, the majority carriers (holes) are repetted back into the substitute, it the surface of p type substitute is deputed. Since the source is devoid of any sometiment of p type substituted to conduction bet the source is drain is not created to conduction bet the source is drain in not created to conduction bet the source is drain in not created to conduction bet the source is drain in not created to conduction bet the source is drain in the source is dr

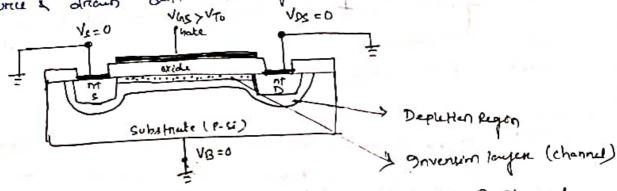

Assume the VGs voltage is further increased. As soon as the sunface potential in the channel region reaches \_ QFP, Sunface sunface potential in the channel region of type (auger will form inversion will established & a conducting of type (auger will form but source & drain difficient region as shown held fig.

(Formation of an inversion (ayer (channel) in an n-channel enhancement - type messer)

connection but two nt regions & it allows current flow, as long as there is a potential 7 This channel new provider an electrical difference the sound a drain terminal voltage

\* The value of Vois voltage needed to cause sunface invention is called Thrushold voltage VTo. -> Thus the MOSFET can conduct no current bet sounce a drain terminals unless Vas > VTO.

The Thrushold Voltage:

IThe value of source to Grate Voltage Vac needed to came sunface invention is called "Thrushold volterye" denoted as VTO.

-) The four physical component of Thrushold voltage: i) The work function difference bel outed channel - Que ii) The Gate voltage component to change the sunface potential ii) The Gate voltage component to offset the depletion region change ivy The voltage component to officer the fixed changes in the gate oxide & in the silicen oxide intenface.

For zero substrate bias, the thrushold voltage VTd ig

$$V_{TO} = Q_{GC} - 2Q_F - \frac{Q_{BO}}{Cox} - \frac{Q_{OX}}{Cox}$$

For non zero substrate bias,

The General form of Thrushold Voltage

$$V_T = V_{T0} - \frac{QB - Q_{B0}}{c_{OX}}$$

The most general Expression for Thrushold Voltage, VT

$$V_T = V_{T0} + \gamma \left( \sqrt{1 - 2\alpha_p + v_{SB}} - \sqrt{12\alpha_p} \right)$$

where  $Y = \frac{129. NA. Esi}{Con}$  is the substrate hias (body effect)

Where . Quet Work function difference been Gate a channy & GBO7 Depletion legion change dentity at sunface invention = - \29. NA. Esi. (-20)

QB = The depletion region change density as a function of QB = - [29. NA. Es: 1-20++46] Gate oxide capacitance = Eox doping concentrat? It ptype material Gate oxide thickness. , q = electron change = 1.602 x 1019 Eax = Fermi potential = KT on (Nsub) T= Roum Temperature K = 1.38× 1023 gothinure carrier conuntration = 1.5 × 10 / Head = doping conuntration MOSFET Openation: A Qualitative View. of The mosfer consists of a Mos capaciton with two Pnjurickin placed immediately adjust to the channel region that is controlled by the Mos Gate -) The contrier i.e electrons in an notes transistin, enter the structure through Bounce & leave through Drain & are Subjected to the contra) of Gate voltage. of To encure that both P-n junctions are revenue hiered initially , the substrate potential is kept lower than the other three terminal potential 1 When OLVGS (VTO, the gated region but? sounce & drain is depleted, no connier flow con he deserved the channel. 27 As gate voltage increased beyond the thrushold voltage (VasyVTO). the mid gap energy level Ei at the sonface of paper below the 7 Semiconductor (Si) Phyla oxide Ee - conduction band Metal (AL) Et -> Intrincie fermi lucy Efp -> Fermilare

(Energy band Diagram of Mos)

EV -> Valance band

causing the sunface potential OR Rs to turn positive & intertion

- Once the invention layer is established on the sonface, an n-type conducting channel forms bet the SRD, which is carrying drain when .

-brium exists in the invented channel region & ID 2x equal to zero.

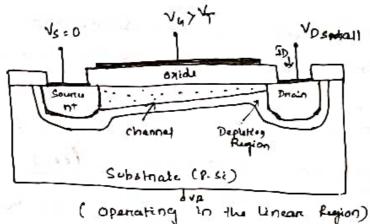

Fig:

Sp propertional to VDS will flow From S to D through conducting channel. The invention layer is the channel forms a contineous current path from S to D. This operation make is called "linear mode" or "linear Region." Thus in linear region operation, the channel region acts as a voltage-controlled revision.

As the drain voltage is increased, the invention byer change charge & the channel depth at the drain ends stantto deeman.

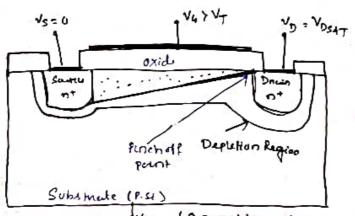

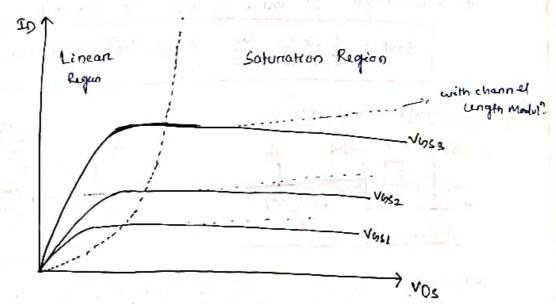

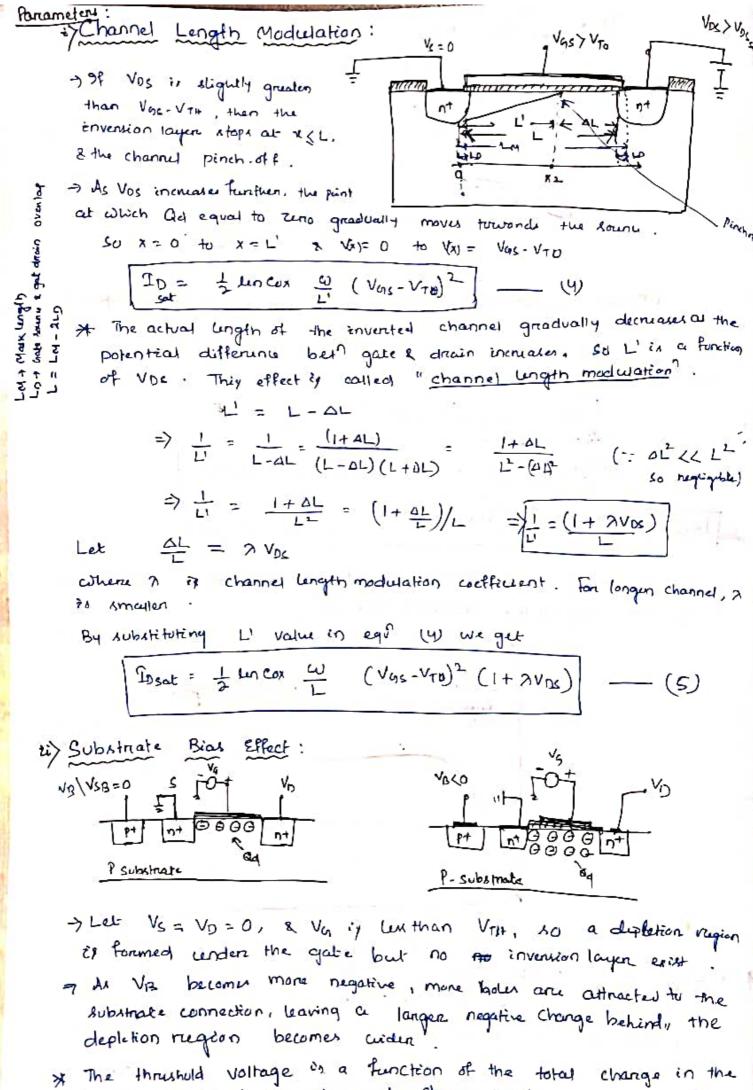

\* For Vos = Vosat, the invention tagen charage at the alrain is reduced to zero, which is called "pinch off point".

The (Openating at the Edge of Saturation)

for VDS > VDSAT, a depleted sunface region form adjacent to the drain & this depletion negron grows towards the S with increasing drawn voltage.

- -> This openation mode of Mosfer is called "saturation mode" on Saturation region".

- of this rigion effective channel length is reduced as the invention layer near the drawn vanishes.

- of the excus voltage drop (VDS-VDSA7) & a high field region forms beto the channel end & the drain boundary.

Fig:

( operating beyond saturation)

\*

MOSFET

Current - Voltage

charicteristics:

Consider a semiconductor bar carrying a current I. If the change density along the direction of current if ad coldombs per meter & the velocity of the change is uneter per (second, then

I = Gd. V We know that Q = CV

t.e Qd = Wcox (VGS-VTB)

Cox in multiplied by W to represent the total capacitance per unit length - cox + Gate oxide capacitance per unit area, Wa channel width.

That the drain voltage is greater than zerro. So the local voltage & difference bett gate a channel varies from V6 to V6-VD

Thus the channel clenkity at a point x along the channel can be written as

Qd(x) = WCOX [VGS-V(x)-VTO]

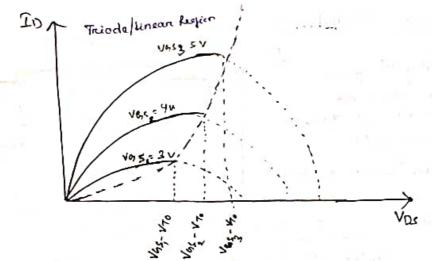

Where V(x) is the channel potential at X Now wrent is given by ID = - INCOX [VGS - V(X) - VTO] V where the -ve sign is intended because the change charriers are negative & I denote the velocity of the current in the channel We know that [U= HE] when I is the mobility of charge curviers & Eis the Electric field  $E(x) = -\frac{du}{dx}$ ( the mobility of electron : len) By substituting this ID = Mcox [Vas-V(x) - 40] len du Due to boundary condition V(0) = 0 V(L) = VDS Multiply both side of a performing integration we get { ED dx = [ Wear lin [ VGs - V(x) - YOr ] d V(x) Since In in constant along the channel IDL = Willin Cox Jus [VGS-V(x)- VTO] elver) => ID = Les cox W [(VGS - VTB)VDS - 1 VDS] - (1) => ID = <u>Lin cox</u> \( \text{2} \left[ 2 (VGS-VTO) VDS - VDS \right] \( \text{2} \) This equ' can also be correcten as  $I_D = \frac{k'}{2} \frac{\omega}{L} \left[ 2 \left( VGS - V_{TO} \right) VDS - V_{DS}^2 \right]$  $\int D = \frac{k}{2} \left[ 2 \left( VGS - VTO \right) VDS - VDS \right]$ Where k = lineax x k = k' W W - Aspect Ratio Vas-VTO = Overdrive Voltage on effective voltage. × 98 VDS < VGS-VTO , the device operates in Triode Region on

drain sounce voltage in linear Region) ( Drain current Venues

Beyond the linear rection on Saturation region

Thus, the drain current to becomes a function only of the gate- Counce voltage vas, beyond the saturation boundary

( saturation of drain wount.

Channel Approximation (GCA): \* Gradual

-> Substrate & Sounce are connected to same potential, NBB=0 -> VI is constant through out the channel of the electric field Ex is more prominent than Ey.

channel length it sub micron range i-e nanometer.

deplection region because the gate change must minnon ad before

an invention layer to formed.

\* Thus, as VB drops, eld increases. Vist also increases. This is called "body effect" on the "backgate effect.

- With body effect

Where P = 129 Es: NSUb/ Cox denotes the body effect wefficient of typically lies to the mange of 0.3 to 0.4 1/2

50

$$\Omega(\text{lin}) = \frac{\text{lin}(\alpha x)}{2} \cdot \frac{\omega}{L} \cdot \left[ 2 \left( V_{GS} - V_{T}(V_{SB}) \right) V_{DS} - V_{DS}^{2} \right]$$

$$\Omega(\text{sur}) = \frac{\text{lin}(\alpha x)}{2} \cdot \frac{\omega}{L} \cdot \left( V_{GS} - V_{T}(V_{SB}) \right) \left( 1 + \lambda \cdot V_{DS} \right)$$

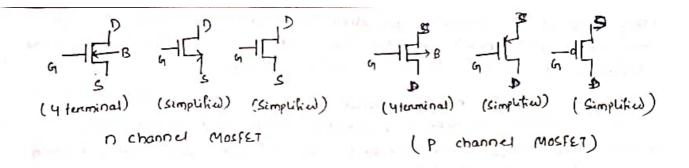

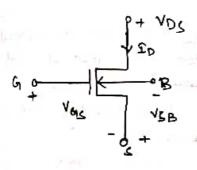

Terminal Voltage & connent of the nows & pros transistom?

(n-channel MOSFET)

( P. channel Mosfer)

Current - Voltage equotion of the P-channel MOSFET:

ID=0 for Vasy VT

$$SD(Sat) = \frac{Lepcox}{2} \cdot \frac{\omega}{L} \left( Vos - V_1 \right)^2 \left( 1 + \beta \cdot Vos \right) \quad for \quad Vos \leq V_1$$

$$= \frac{Vos}{L} \cdot \frac{Vos}{L} \cdot \frac{Vos}{L} = \frac{Vos}{L} \cdot \frac{Vos}{L}$$

Fun n-channel MOSFET:

# Mosfet Scaling & Small- Geometry Effects:

- > The design of high density thips in Mos VLSI technology requires that the packing density of MOSFETZ wed in the okts in as high at possible, consequently that the size of transcisions are as small as possible.

- I The reduction of the eige, i.e the dimensions of Mosfets, is Commonly referred to as scaling. If is expected that the operational characteristics of the cros transactor will change with reduction of the dimension.

- -> Scaling of Mos transistors is concerned with Systemic reduction of overall dimensions of the devices as allowed by available technology, while preserving the geometrie reation found in the larger device.

- I The proportional soling of all devices in a ckl would certainly rusults in a reduction of the total silicon area occupied by the CKt, thereby increasing the overall functional density of the chip.

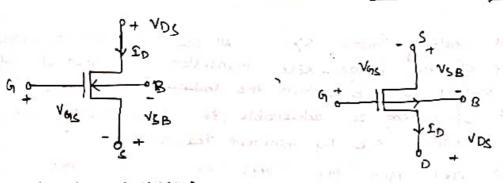

- A constant scaling factors Syl. All the horizental a vertical dimensions of the large-size transistors are then divided by this scaling factor to obtain the scaling Scaled device.

- -> The extent of scaling in achievable is determined by the fabrication technology i-e by minimum feature eine.

1991 1993 1995 1997 1999 years 1985 1987 1989 0.8 0.5 0.35 0.25 Feature (re(um) 2.5 1.7 1-2 1-0

( Scaling of MOSFET by a scaling factor of S) The scaling of all dimensions by a factor of SYI hade to the methodion of the area occupied by the transistor by a tactor of 5.

I There are two basic types of size-reduction strategies: full Scaling (also called constant field scaling) a constant - Voltage scaling.

- i) Full Scaling ( Constant field Scaling):

- This scaling option attempts to preserve the magnitude of internal electric fields in the mosfets, while the dimensions are scaled olive by a factor s. To achieve this, all potential must be stated down proportionally. By the same scaling teston.

- -> Pocker equal describe that the change density must be incurated by a factor s in order to maintain the field conditions.

### Influence of tell scaling:

| avantity                | Belone Scal | ing         | After Scaling           |

|-------------------------|-------------|-------------|-------------------------|

| i) channel length -     |             |             | L' = L/S                |

| is channel width -      | _ N -       | x           | M = MIE                 |

| in Gate Oxide thickness | - tox       |             | tox' = tox [s           |

| ivy Junction depth      | x;          |             | $x_j = x_j   s$         |

| vy Powen Rupply Voltage |             |             | NOD = NOD IT            |

| VI) Thrushold voltage   | VTo         |             | VTO = NTOLS             |

| vil) Doping densities   | NA          |             | ND = S. ND $NX = S. NA$ |

| vii) Oxide capacitanu   | cox         |             | Cox = 5. Cox            |

| 1x) Drain Current _     | ID.         | Ke ITPEL IX | ID = ID                 |

| x) Power descipation    | - P         | 1           | p' = P/52               |

| xy power density        | - P/Ania    | 0 - 1 3 4   | P'/Ario = P/Area.       |

- 7 The surface mobility han, expect nation W/2 will runain unchanged under scaling.

- If The power dissipation is an attractive features of full staling.

With the device area dissipation reduction by 52, the power density per unit area temporally virtually unchanged for the scaled device.

- i) Constant Voltage Scaling:

- be scaled down proportionally with the device dimensions the

- In particular, the periphenes a contentace cincitary may trequire certain voltage levels for all input a output voltages, as a complicated level shifter arrange ments. For these reasons constant voltage scaling or usually preference over full scaling.

of the MOSFET are reduced by a foctore S. The powersupply voltage 2 the terminal voltages, on the other hand, rumain unchanged.

In order to preserve the change field region.

| A Quantity            | Before Scaling | After scaling                                            |  |

|-----------------------|----------------|----------------------------------------------------------|--|

| i) Dimensions         | ω, L, tax, xj  | Reduced by S ( W = W/s, tox = tox S<br>L' = L/s, xj = xi |  |

|                       |                | 2 (2                                                     |  |

| is Voltage            | VDD, V1        | Remain unchanged                                         |  |

| ii) Doping denviku    | CIA , 417      | 300 mared by 62 (N/ = 52. NA<br>ND! = 62. ND)            |  |

| iv) Oxide capolitanu  | Cox            |                                                          |  |

| V> Drain current      | ID.            | Cox' = S.Cox                                             |  |

| Vi) Power Discipation | Ρ              | $\hat{\mathcal{L}}_{D} = S.\hat{\mathcal{L}}_{D}$        |  |

| vii) Power density    | PLARLO         | $P^1 = S.P$ $P^1 = S.P$                                  |  |

|                       | 0.2            | PYAnea = 53. P. Anea                                     |  |

\* This scaling may prefered over feel scaling in many presented cases because of the external voltage level constraints.

H This scaling increases the dirain current & power density by a factors? When causes Serious reliability problems for the Scaled transiston such as electromigration; but carnier alignadation, exide breakdain a electrical over struss.

## wix Short channel Effect:

7 A MOSFET can be defined as a Short-Channel device if the effective channel length 'Lift' is approximately equal to the lowner a drain junction depth 'xi'.

The short-channel effect arises in this case one attributed to two physical phenomena is the limitation imposed on electron drift characterities in the channel ii) The modification of the thrubold voltage due to shortening channel length.

## Myx Clarenow - Channey Effect:

- -7 Mos transistons that have channel width hi on the same order of magnitude as the maximum depletion trugion thickness Xdm are defined as narrow channel device.

- The most eignificant narmow channel effect is that the actual thrubuld voltage of such denice is larger than that predicted by the conventional thrushed voltage formula.

VTO [narcrus channel] = VTO + A VTO.

## huran

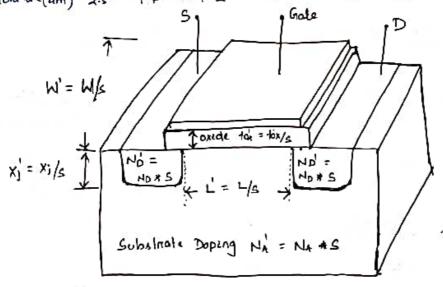

### MOSFET Capacitances:

not lumped but distributed.

- \* Based on their physical origins, the panasitic device capacitates can be classified into two major groups:

- i) Oxide rulated capacitanus

- ii) Junction capacitanu.

## => Oxide-Related Capacitances:

The gate electrode overlaps both sound sugion & the chain region at the edge. The two overlap capacitanus that arise as a rulest of this structural arrangement are called Cap (overlap) & Cas (overlap) respectively.

Cystoverlap) = Cox. W. LD | Cystoverlap) = Cox. W. LD |

Both somethe a direct have

with  $Cox = \frac{Eox}{Iox}$

Both of these capacitanes are voltage independent.

Cgs = hate to Sound capacitanus

Cgd = 11 11 Drain 12

Cgb = 11 11 Substitute 18

These are voltage dependent,

(1) 90 "cut off mode" sunface is not invented . There is no conducting channel.

So [Cgs = Cgd = 0]

Cgb = Cox.W.L

2

3 90 "Saturation mode", the inversion layer on the sunface downs extend to the obtain, but it is pinch off.

The sum of all 3 voltage-dependent (distributed) gate-oxide

X Capacitanus (Cgb+ Cgc+ Cgd) has a minimum value 0.66 CoxUL

(in saturation) a maximum value of Cox.W.L (in cut off)

Unearl)

7 For simple calculation, all 3 corparitanus are considered as connects

1 parallel & a constant worst case value cas. WL L+2LD) (an he

liked for sum of Mosfet gate oxide capacitans.

# ii) Junction Capocitanus:

- 7 The Voltage-dependent source-substrate & drain-substrate function capacitanus, CSb & CdL respectively.

- -> Both these capacitances, and are due to the depletion charage scarcacanding the respective Source are drain diffusion regions embedded in the substitute.

- operating conditions of the Mosfell & that the amount of junction capacitance is a function of applied terminal voltages.

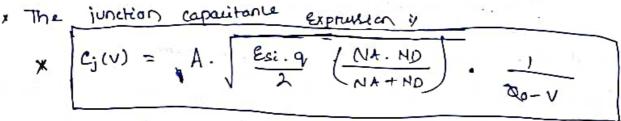

on General Forem of junction capacitary

$$\frac{C_{j}(v) = \frac{A \cdot C_{jo}}{(1 - \frac{V}{B_{o}})^{m}}$$

where A = junction area.

Ro = Built-in junction potential = KT in (NA. ND)

m = Grading coefficient , to m= 1 for obscupt junction = 1/2 for Unearly gradul

Cjo = The Zerro hiar junction capacitana perz unit arua

-> The equivalent large signal corparitance -> (i-e change in him conditing

$$Ceq = -\frac{A \cdot c_{j0} \cdot a_{0}}{(v_{2}-v_{1})(1-m)} \left[ \left(1-\frac{v_{2}}{a_{0}}\right)^{1-m} - \left(1-\frac{v_{1}}{a_{0}}\right)^{1-m} \right]$$

Ceq is always calculated for a transition bet two known voitage

lends. ( Let the trevens voltage changes. VI to V2)

on lead = \frac{1}{V\_2-VI} \big(^{V\_2}\_{VI} e\_j(V) dV \cdot \frac{1}{VI}

A Assume that the Side wall eloping density is given by NA(SW), the Zeno bias capolitance pen unit area can be

$$Cjos\omega = \sqrt{\frac{Esi.q}{2}} \left( \frac{NA(s\omega).ND}{NA(s\omega)+ND} \right) \cdot \frac{1}{80s\omega}$$

Whene Dosw is the built in potential of side wall junction

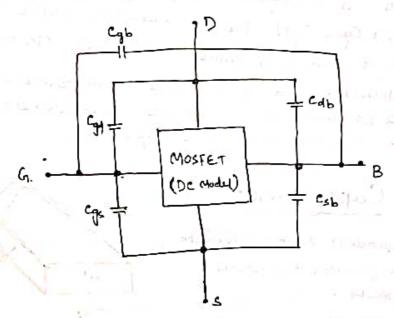

# Modeling of Mos Transiston Using Spice:

\* Spile (Simulation program with Integrated (Kt emphasis) is a general purpose cht simulator which is used very widely both in the meroelectronic indutry a educational gostitution for cht duign.

of the SPICE software had 3 built in MOSFET models:

Exell (MOSI) is described by a square low connect Woltage characteristics.

ii) LEVEL 2 (MOS2) is a detailed analytical MOSFET mode ii) LEVEL 3 (MOS3) is a Semi empirical model.

7 Both MOS2 & MOS3 Enclude 2nd order effects such as shout channel thrushold voltage, Subthrushold Conductions Change control capacitance scattering United Velocity Saturation etc.

Cno

+ 145-

# \* Basic Concept:

- The equivalent ckt structures

of NMOS LEVEL 1 moder;

X Which if the default Mosfer

model in SPICE is shown.

7 The Balic Structure & also

- 7 The Balic Structure & allo typical for the LEVEL 2 & LEVEL 3 models.

- The voltage controlled current Source ID determines the Steady state current-voltage behaviour of the davice.

( Equivalent ckt Structure of the LEVELI MOSFET model in SPICE).

CSD

- The voitage controlled (nonlinear) capacitores connected befithe terminals represent the paraditic oxide-related & junction with

- 7 The source-substrate & the drain-substrate junction, are revenue biased under normal co-operating conditions are represented by ideal diodes in they equivalent the

- > Finally, the paracitic fources drain ruistances are prepresented the ruiston to & the respectively, connected between the drain connected between the drain

He basic geometry of an LMOS transiston.

Can be described by specifying the nominal channel (gate) length

L & the Channel width W, i, t, both of which are

indicated on the element description line.

The channel width Wish by definition, the width of the area covered by the thin gate oxide.

The effective channel length Left is defined as the distance on the sunface been the two (source & drain) diffusion regions.

-> Thus in order to find the effective channel length, the gate-source overlap distance a gate-drain overlap distance must be subtracted from the nominal (mark) gate length specifies on the device description line.

The amount of gate ovenlap over sounce & drain can be specifical by using the lateral diffusion coefficient LD in Spice.

He fore modeling P channel mox transistors, the direction of the dependent current Source, the polarities of the terminal voltages, & the direction of two diodes represently the source. Substrate a the drain-substrate junction must be treversed.

and the same of th

Property of the second

# \* The LEVEL1 Model Equations:

gntroduction:

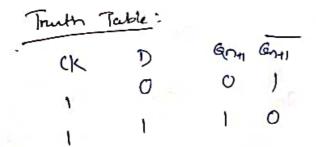

|     | A    | В   |    |

|-----|------|-----|----|

| 1.  | O    | 1   |    |

|     | 1    | 0   | 1  |

| (Tr | tuth | tab | u) |

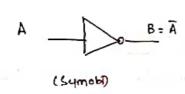

790 Mos inventure, both input variable A ≤ ofe variable B are represented by node voltage, referenced to ground potential.

Justing possitive logic convention, the Boolian (logic) value of 'I' can be represented by a vors & logic 'o' represented by low voltage O.

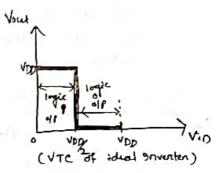

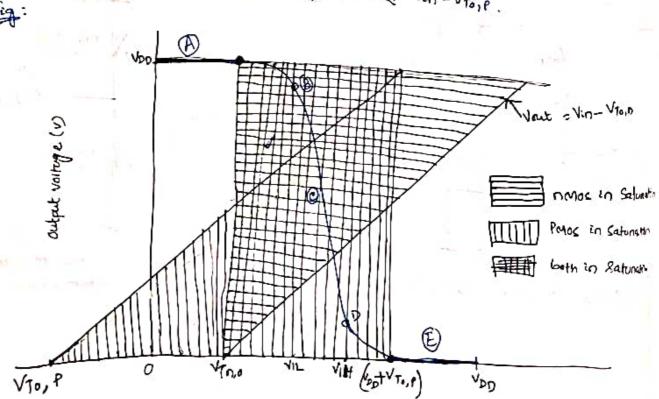

-> The De voltage transfer is (vie) of ideal inventor is shown in the

-The Voltage VTIH is called inventer Thrushold Voltage. For any ilp voltage bet 0 & VTH = VDD/2, the old voltage equal to VDD (togic) The output switches from Voo to owher ilp equal to Vm.

+ For Any ilp voltage been Vitt & VOID off assumes a value o.

of Thus an input voltage of Vin < Vm is intersprented by this edial inventer as logic 0 & input voltage Vinc Vinc Von if interprented by as logic 1

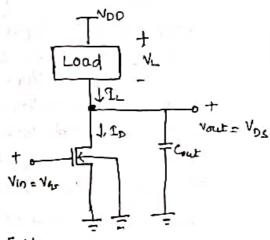

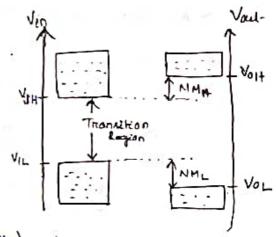

## NOMOS 9 nventens:

I The input voltage of the inventer ckt is also the gate - to- Source voltage of the nows transistor (Vin = Vas), while the output voltage of the ckt ix equal to the drain to sounce voltage (vout = Vos).

I The sounce a the substrate terminals of the nows transcritor, also called the driver transistor, are connected to ground potential, hence Source to substrate voltage in VSB=0.

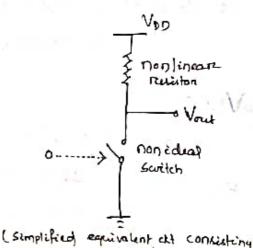

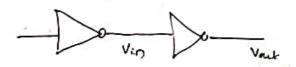

Fig. (General CK+ Structure of an nows inventer.)

-> 90 this generalized representation, the load device is represented as a two-terminal cut element with terminal arrunt IL & terminal Voltage VL (IL).

I One terminal of the load device is connected to the drain of n-channel MOSFET, while the other terminal is connected to VOD, the powers Supply Voltage

- The characteristics of the inventer ext actually depend very strongly a upon the type & cls of the load device.

- for all preactical purposes, there will no connect that into one out of the input & output terminal of the inventor in De steady state.

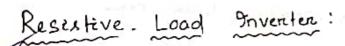

# Voltage Transfer charecteristics (VTC):

Ext (Figs), the load comment is equal to most drain women).

Lo (Vin, Vout) = IL (VL)

-> The VTC describes Vout as a function of Vin Under De condition

VoH

VOL.

dreat =-1

dveit =-1

- The output voltage Vau- is equal to the high value of Von (output high voltage)

- -) In this case, the driver notos transiston is in cutoff, hence does not conduct any current.

- of As Vin increases, the driver transister starts conducting a certain drain connent & Vout Starts to decrease.

- There are two critical points on VIL Vih VIH VOHT this conver, where slope of the Vout (vin) ( VTS of news Transister) als becomes equal to -1.

i.e dvan =-1

- -) The smaller input voltage satisfy this condition is called input low voltage VIL & the larger vin Satisfy this cool is called input high voltage VIH.

- -> When vin = VOH, the att drops reach a value VOL.

- of the invented thruhold voltage Vth is considered as the transition voltage of defined as the point where Vin = Vout on the VTc.

The Functional definitions are:

VOH: Max output Voltage when the output level is logic 1

VOL: CMEN" " " " " " " " " O

VIL: Max support in which can be interpreted as logico'

VIII : CHEN' " " 11 " " " 1

Noise Mangins:

of the ckt noise in the unwanted lignal

The noise tolerance for digital cht called noise mangin, denoted by Nm.

of the noise immunity of the ckt increases with NM.

-> Two noise mangin will be defined: the noise mangen for low eignal level (NML)

2 the nrise mangin for high signal level (NMH)

of Generally Vout = f(vin)

when noise is added to input

By Taylon Services

Vout = f(ven) + dvout. Avnoise + higher order terms neglect.

So Persturbed output = Nomenal output + Gain X External Persturbation:

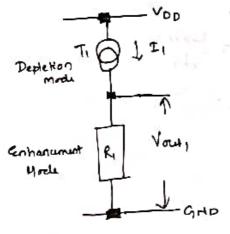

of Here an enhanument-type notos

thankiston act as driven the & a limb

unean number RL act as load.

790 De steady state openation ID = IR.

-> VSB = 0 as source & Bostnate 18 grandu

-> of Vin < VTO, inanciston of cuttoff thene dismit conduct any comment.

Vout: VOO-IDEO\_

transistan start conducting a nonzero drain connecting.

(The noise mangen as

NML a NMH. The

Shaded regions

indicate valid high &

Inco Levels of ilp & olp

signal.

Resintive - load government cht.

#### Calculation:

Let us assume Vin = Voh = VDD.,  $Vont = VDS = Vol_$ As  $Vin - V_{TO} > Vout$ , transiston operates in linear rugion.

VIL: When Your > Vin - Vto, transiston operate in saturation Von-Vout = Kn (Vin-VTO)2 differentiate both side w.n.t Vin it separat to t - 1 avoid = Kn. (Vin-V70) the derivative of output voltage w.n.+ input voltage equal to (-1) at VIL, By substituting they - I (-1) = KO(V+2- VTO) =) VIL = VTO + KORL So vout in, vous (vin=VIL) = VDD- KOPL (VTO + L - VTO) => Vout (Vin = VIL) = VOD - ILAPL When Yout < Vin-VTH, transiston operates in Linear Region. VIH : IR = ID => VDO-Vout = Kn [2 (vin-VTO) Vout - Vout] differentiate both side w.n.t ven - I avout = Kn [2(vin-vio) dvout + 2vout - 2vout . dvout ] When Vin=VIH, dvant =-1, by subtistiving this - 1 (-1) = Kn [(ViH - VTO) (-1) + 2 vant] > TVIH = VTO + 2 VOW - KARL VOD-VOW- = K2 [2 (VIO+2 VOUX-1 K2RL-VIO) Voux- Voux] ) By substituty they value. Volt (V:n = VIH) = 1 3 Kn. P VIH = VTO + \ 3 KORL Again by substituting

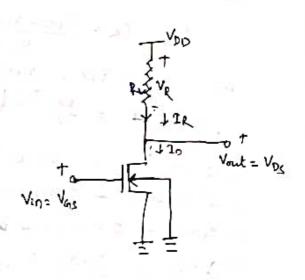

# governiers With n. type Mosfet Load:

- 7 As the silicon area occupied by the transcator is smaller than relistive load, so Mosfet in used as load device.

- -> Enhancement-load nmos inventens are not used in large scale digital application as it suffers from rulatively high stand by (Dc) power dissipation.

#### nmos goventen: Depletion. Load

Advantages of deletion-load inventors

i) Sharp VTC transition a better noise mangin

ii) Single power supply

iii) Smaller overall layout area.

(9 nventers ckt with depletion type n-Moslow)

fransiston with VTO, wad (0.

a nonlinear load rullion a nonideal switch controlled by the inpur) type n. mos transiston, with 7 The driver device is an enhancement To, driver 70, whenever the load is a depletion-type nones

- -> The gate & sounce nodu and of the load transiston are connects 30 Vas, loud = 0 always.

- -> He thrubold voltage of depletion type load is negative, Vasionay VT, law in saturfied & load how a conducting channel regardless of input, outper

- 7 Both the transistons are built on the same p-type substrate which of connected to growns. The load device in subject to the Substnate- biasseffect, so that its tubeloate thrubold voltage is a function of its sounce to substrate voltage). VSBloud - Vout.

VI, wand = VTO, wand + V (V[20 F] + Vout - [120 F]) -> When Yout < VDO + VT. wad , the load transiston is insofunction T. e VDS local 7 Vins load - VT, local theo To, wed = kn, wed [- VT, loud (Voul)] = kn, knd . | VT, wed (Voul) For Voul 7 VOD+V71000, local transisters is in them region 10, 1000 = knolow [2 / V7 1000 (Vout) (VOU-Vout) - (VOD-Vout) The VTC of they inventer can be constructed by setting, 10. driver = ID. load Vos, driver = Vin Vos, driver = Vou Calculation: VOH : , then driven in cutoff 2 not conduct connect. But load transiston operator in linear hugen When Vin & VTO, draven has also zeno drain woment. Let forward = Our substituting Voti = Vout ID, wad = Kn. 10ad [2/VT, Youd (VOH)] (VOD-VOH) - (VOD-VOH)]=0 The only valid Galution in linear region is Voit = VDD VOL = Vin = VOH = VOD . So driven openates in knear ? loud in saturation IDIONED = Indriver Kdriver [ 2 (VOIT - VTO). VOL - VOL] = KIOND [ - VT IOND (VIL)] VOL can be solve by temponarily neglecting the dependence of You

VOL = VOH - VTO - V(VOH - VTO)2 - KIOW . | VT. IOWS (VOL) = 2

```

-> The slope of Vie in (-1) is dvait =- 1 when

Here driver operates, saturation while load operate in linear

By KCL Indriver = IDION

Kdriver (van-Vro)2 = kinw [2] Vr. inw (voul) (VOD-Vout) - (VOD-Vout)

differentiate both lide with w.r.+ Vin

Kdriver (Vin- V70) = Kirw 2 /2 /VT, loud (Vous) (- dVout) + 2 (VOD-Vout)

(-dVI, Iow) - 2 (VOD-Vout) (-dvat)

Here divis of negligible wint others & substitute VIL for Vind

put dvoit =-1 ,

VIL = VTO + Klow [ Vout - VOD + VTION (Vant)]

VIH:

Here driven operates in linear & load operates in Saturation.

Indriver - In www

=> Kariver [2 (Vig-VTO). Vout-Your] = Klow [- VTIDW (Vout)]

Differentiating both seds w.n.t Vin

Kdriver Vout + (Vin-VTO) avout - Vout din)

= Kloud [- V7,1000 (Voul)] ( dVTloud) d Vout

a Vout/oven = -1 & Vin = VIH

Substitute

VIH = VTO + 2 Vout + Klow . [- VT, 1000 (Vaut)]. ( d VT. 1000)

```

Hene avr. 1000 = 2 Part + Vous

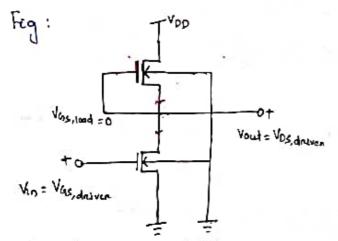

# Mos Inverden =

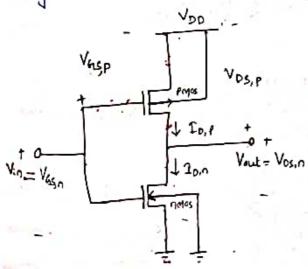

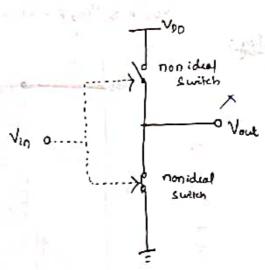

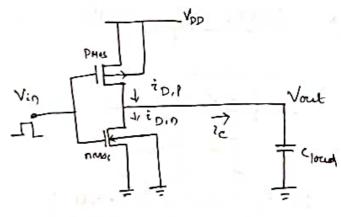

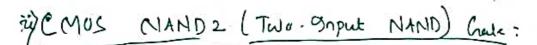

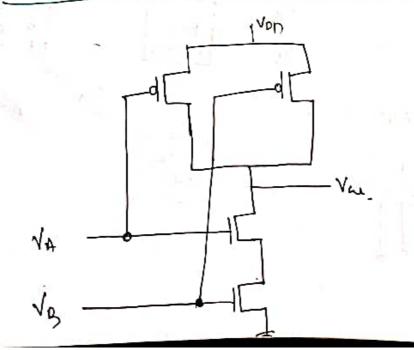

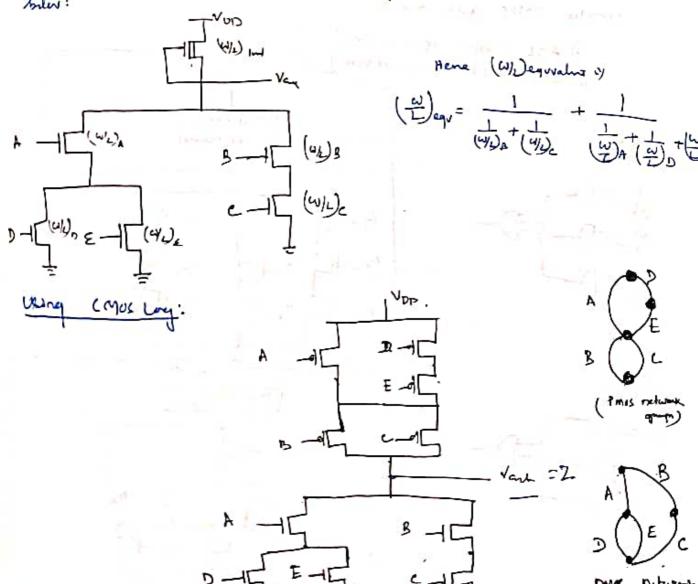

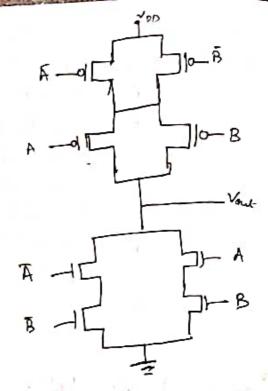

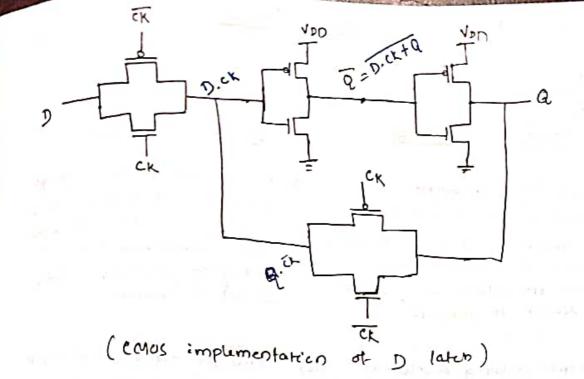

- An inventer which is consists of an enhancement type nmos transiston & an enhancement type pmos transiston, operating to complementary mode to called complementary Mos (CMOS).

- The ckt topology is complementary push-pull in the densethet for high input, the nmos transistor driver (pulls down) the output node while the pmos transistor act as load, a for low input, the pross transistor driver (pulls up) the output node while n mos transistor act as load.

#### Advantage:

- i) The Steady state power descipation is ventually negligible except for small power dissipation due to leakage connect.

- ii) The VTC exhibits a full output voltage swing bel? or & VOD. & that the VTE transition in Usually very chang. Thus VTE of the cours invented trusmally that of an ideal inventer.

### Cincuit Openation .

Fig:

(CMOS Goventen Cinuit)

(Simplified View of the CMOS enventer, consisting of two complumentary consider suitches. The substrate of the norms transition is connected to the ground, while the substrate of the pros transition is connected to the prosent supply voltage. VDD, in order to reverse bias the sound & drain junction.

From the ckt:

also

$$V_{OS}, \rho = -(V_{OD} - V_{IO})$$

$\left\{ - (V_{DS}, \rho = -(V_{OD} - V_{OUL}) \right\} - (2)$

- openating in linear negion.

- -> Since IDn = Io.p=0, Vos, of proses also equal to zero

Lo Vout = VoH = VDD

- Thun Vin exceed (VDD+VTO,P), pmog tann off & nmos operates in linear region, but VDS,0=0 due to for=100=0.

- if the following condition is satisfied.

Vos, n > Vas, n - Vro, n > Vout > Vin-Vro, n

PMOS transmore operatus in Saluration if Vin < (Von+Vro, P) & if

Vos, p < Vas, p - Vro, p > Vout < Vin - Vro, P.

Openating rugions of the nows & I Mes Tremiston

```

Calculation of VIL:

```

power operates in linear region.

Differentiating both lide w.n.t Vin

$$kn (Vin - V_{To}, n) = kp [(Vin - Vop - V_{To}, p) \frac{dvaut}{dvin} + (Vout - Vop) - (Vout - Vop) \frac{dvaut}{dvin} + (Vout - Vop)$$

Substituting  $Vin = Vil = 8 \frac{\partial Vout}{\partial vin} = -1$

$$kn (Vii - Von) = Vol = 8 \frac{\partial Vout}{\partial vin} = -1$$

where

$$k_R = \frac{k_D}{K_P}$$

.

### VIH :

When Vin to VIH mos operates in linear regions.

where KR=Kn

Velay Time Deliniti

1.1

When

$$V_{in} = V_{in} = V_{out}$$

both nows a page operate in the saturation region

so  $\frac{Kn}{2} \left( V_{0s,n} - V_{To,n} \right)^2 = \frac{Kp}{2} \left( V_{0s,p} - V_{To,p} \right)^2$

=>  $\left( V_{in} - V_{To,n} \right) = \frac{Kp}{Kn} \cdot \left( V_{in} - V_{DD} - V_{To,p} \right)$

$$V_{th} = V_{To,n} + \frac{1}{K_R} \left( V_{DD} + V_{To,p} \right)$$

$$1 + \int_{K_R}^{T}$$

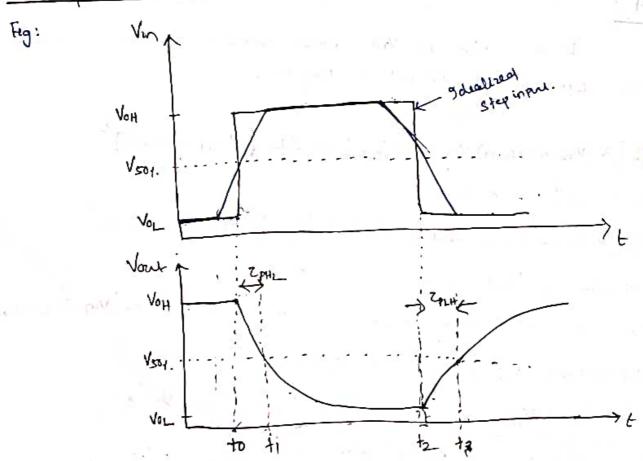

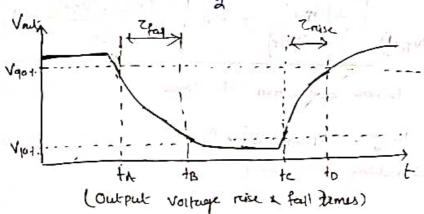

## Delay Time Definitions:

(9) put: 8 autant voltage waveforms of a typical inventore & the definitions of enopagation duly times. The input voltage news ig idealized as a step pulse for simplicity)

combined capacitance of the output node will be called the capacitance. wad

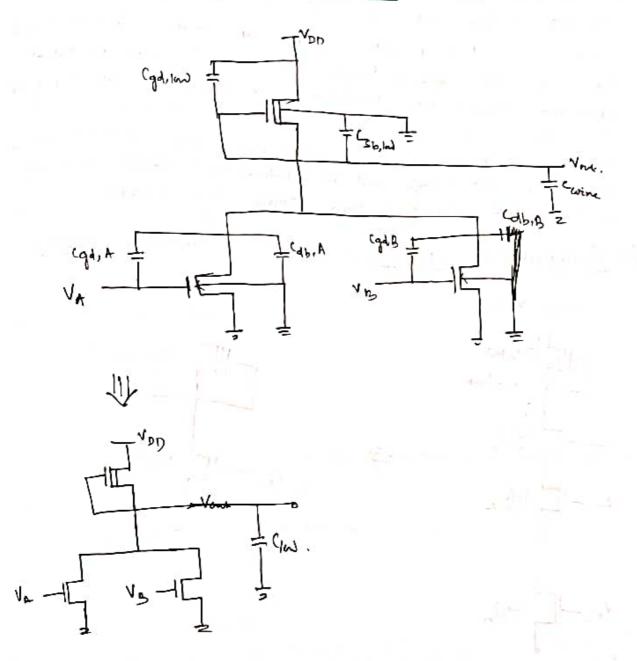

Croad = Cgd,n+ cqd,p+ Cdb,p+ Cdb,n+ Cin++ Cg where Cent = Lumped interconnect Capacitanu Capacitance due to thin oxide

19.

Total: is the time delay between the Vsot transition of the ressing input voltage & Vso 1. Irrancition of the falling output voltage!

Epult: is the time dulay bet the Vsot transition of the talling input voltage & V50 +. transition of the reseng output voltage.

Tp: Avenage propagation dulay

\*The ruse time Truse to defined at the time required for the output voltage to rise from Viot level to Vgot level.

# The "Fall Time" Efall is defended as the time required for the output voltage to drop from Vgot level to 40+. level.

$$V_{10+} = V_{0L} + 0.1 (V_{0H} - V_{0L})$$

$V_{q0+} = V_{0L} + 0.9 (V_{0H} - V_{0L})$

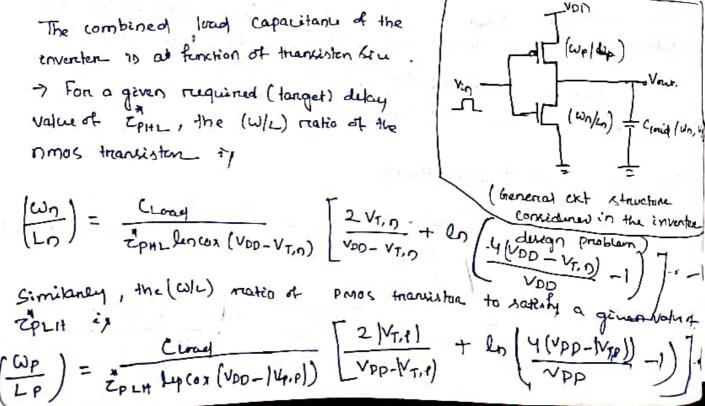

, <u>Calculation</u> of Delay times:

The transistor dimension should be chosen so that all delay times rumain below the required tanget value.

Cint = lumped interconnect capacitans (parasitic capacitans contribution The total capacitive load of the inventor connection better intention

When Keq, n, Keq, P > Voltage equivalence factor.

Cjo,n, Cjo,P >> Zeno hiar junction carpacitore

Clsw,n, Clsw,p >> Side wall jun carpacitore.

Now the delay

$$Z_{PHL} = \frac{1}{100} \left( \frac{d_0 + (d_0 + Rd_p) \omega_0}{\omega_0} \right)$$

When

$$T_{D} = \frac{L_{D}}{4\pi \cos(v_{DD} - V_{T,D})} \times \left[ \frac{2V_{T,D}}{V_{DD} - V_{T,D}} + l_{D} \left[ \frac{4(v_{DD} - V_{T,D})}{v_{DD}} - 1 \right] \right]$$

$$\frac{\Gamma_{p}}{\text{exp cox (Vop-|VT,r)}} \times \left[ \frac{2 |V_{T,P}|}{Vop-|V_{T,P}|} + \ln \left( \frac{4 |Vop-|V_{T,P}|}{Vop} - 1 \right) \right]$$

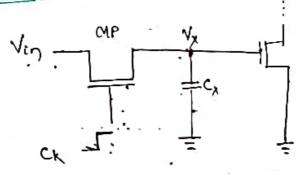

- of An inherent limitation to switching speed in chos inventory due to drain panasitic capacitane.

- 7 Increasing wo keep to reduce the propagation delay times will have a diminishing influence unpointed belong tentain value of the delay value will be asymptocally approach a limit value for large who of the

So

$$\frac{1}{2}$$

$\frac{1}{2}$   $\frac$

- The propagation delay time of a chas inventor cannot be reduce beyond there limit value.

- 7 Thise limit is independent of cent a cq.

#### KKK

# Estimation of Interconnect Parasitics:

by, taking assumption that loads are mainly capacitive & Lumped.

- The conventional dulay estimation approaches seek to classify 3 main components of the output load, all of which are assumed to be purely capacitive as

- i) Internal paracitic capacitances of the transistors

- 2) Interconnect (line) compositances

- 3) Input capacitances of the fan-out-gutes.

- 7 The capacitive/Inductive coupling & the signal interference bet? neighbouring line should also be taken into consideration for accurate estimation of delay.

- -) The gate delay due to capacitive load components dominates the line delay -

- Tour sub-micron technologies, the interconnect delay stants to dominate the gate delay. In order to deal with the implications & to optimize a system for speed, this designer much have reliable a efficient means for

- i) estimating the incomment printerconnect paracities in a large clip

- ii) Simulating the trainent effects.

## Switching Power Dissipation of CMOS governten:

- -> The static power discipation of the CMOS inventor is quite negligible.

- alternatingly changed up a changed down, for which the

onsider a semple errors

inventor ckt which input

voltage of an ideal step

waveform with negligible

rise of tell time.

when the input voltage

switches from low to high, the

pours transistor turn off &

nois transistor stant conducting.

(Cmos inventer www in the dynamic power-dissipation analysis)

-> During this Phase, the crut put low analysis)

capacitance Cloud is if being dischanged through nows transists.

-> Thus the capaciton current equals to the instantaneous drain wrongs of the nows transiston.

M Similarly when the Vin switchs, high tolow, the nos transisten is turn off a pmos transisten termo stants conducting so cloud, stanta changing. Therefore, the capaciten cunnent is equals to the instantaneous drain women't of pmos transisten.

The average power dessipates

Since during switching, the nmos & pmas transistor in a cmos inventer conduct current for one-holf period each, so

The average power discipation is independent of all transition charecteristics & transition sizes.

PDP (Power delay Product): 9t if the avenage energy regions for a gate to switch its of Voltage from low to high 2 high to las.

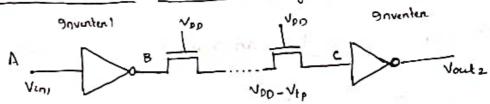

CMOS Ring Oscillator: V 2 V2 V3 V3 I Chard, I Chard, 2 T Chard, 5 PHLZ EPLH3 (fig:1, 3 stage rung ose ckt consisting of identical 9 number/ Typical voltage waveform of thes wenters, -> Consider the cascade connection of 3 identical CMUS inventer where ofp node of 3nd inventer is connected to the ilp node of let inventen. 7 The 3 enventers form a voltage feedback loop. 7 The CKT down't have a stable operating point. The only de point at which the input-output of all inventors are equal to Vth are unstable & any disturbance in node voltages would make the okt drift away From the de operating point. - A closed loop calcade connection of any odd number of inventer would display autable behavion. of such ckt will oscillate once any of the inventor input output voltages deviate from unstable operating point (Vtn). Thenfore the Ckt is called fing obillator. 7 Fig 2 shows typical of voltage waveforms it 3 inventors during oscillation. As the off voltage VI of the 1st inventors reises from Vol to Volt it triggerens the 2nd enventers output V2 to fall from VOH to VOL . 7 The difference bet 1 V50+. Conditioned times of V1 8 V2 in the signal propagation delay ZpHLz of 2nd inventer -> As the ofe voltage of V2 of the 2nd inventor folls, it triggers the Of voltage 12 of the Brid inventor to rise from Volto Volt of Again the differee bet " V501- crossing times of 1/2 of V3 of couled EPLHS a 7 90 the three ckt the oscillator period can be expressed as Sum of the Six propagation dulay time -> Since three Enventeur cene assumed to be identical Close) = Close = Closes T= ZPHL, + ZPHI+ ZPHLZ+ZPLHZ+ PHL3+ZPLH3 = 22p+ 22p+ 22p = 3x2.2p = 62p colum f= Inquiry of oscillation-

> (Rutur Book)

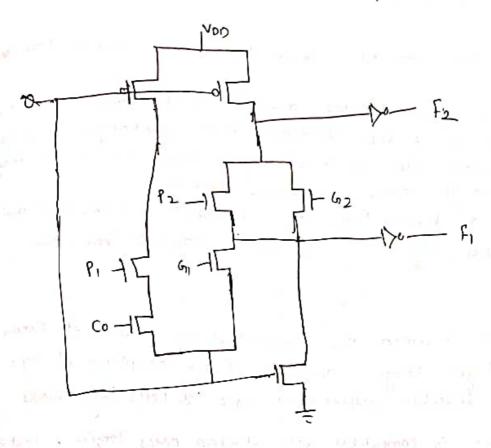

Defermination of Pull-up to pull down Ratio:

if NMOS goventer driven by another mos goverter:

(nonos inventor dreven by another inventor)

- An inventer is driven from the output of another similar inventor , consider the depletion mude transiston for which vgs = 0 under

all conditions. The requirement

For level mangins around the inventor thrushold, we set Vin = 0.5 Vpp At this point both transcritor are in Saturation &

$$Tds = K \frac{\omega}{L} \frac{(V_{HS} - V_{To})^2}{2}$$

gn the depletion mode

Equating (since connects are the same ? we have

where wp.d, Lp.d, Wp.v & Lp.v are the width a length of the pull-down a pull-up transiston respectively.

We have

$$\frac{1}{Z_{pd}} \left( V_{en} - V_{to} \right)^2 = \frac{1}{Z_{pu}} \left( - V_{td} \right)^2$$

By Jubatituting typical values Vt = 0.2 Von; Vtd = -0.6 Voo, Vin = 0.5 Vop (for equal manging)

ii) Nous goventer driver through one or more pass transistor:

(Pull-up to pull-down mation for enventing logic coupled by pass transiston)

- There the input to inventer a come from the output of inventer 1 but passed through one more nows transcriptors used as Switchering Series (cased pass transcriptors).

- The connection of pan transistory in series will degrade the large large I level into inventer 2 so that the output will not be a proper logic O level.

- The critical condition is when point A is at O volta & B is thus at VDD, but the voltage into inventer 2 at point c is now reduced from VDD by the thrushold voltage of the Series Series pass transistors

- 7 With all par transiston gate connected to Vop , there is a loss of Vtp , Since no state evenent flows through them & there can be no voltage drop in the channels.

- -> Therefore input voltage to inventor 2 is Vinz = VDD - Vtop